如果我们已经遵循设计规则检查(DRC),为什么还需要面向制造的设计(DFM)?

客户越来越多地问我们,如果DRC已经嵌入到他们的设计工具中,他们为什么要运行DFM分析。在寻求帮助设计人员创建更好的设计的过程中,我们意识到这一基本原理并不总是很好理解,因此我们开始一劳永逸地澄清DRC和 DFM之间的区别,以及为什么在PCB设计范式中真正需要两者。

在工程设计中,设计规则检查(DRC)可确保PCB布局准确反映电路板原理图中定义的连接性和尺寸公差。这些规则主要定义了整个PCB或PCB上各个层,网络或区域的各种PCB对象之间允许的最小间距。对于设计人员来说,间距 可能会影响电路性能。对于制造商来说,间距会影响制造 或组装PCB的能力。

可制造性设计(DFM)是安排PCB布局拓扑的过程,其方式可以减轻电路板制造和组装过程中可能遇到的问题。用随意的话来说,仅仅因为你可以创建一个特定的设计并不意味着你应该这样做,或者说它是实用的,具有成 本效益的,或者生产起来是可靠的。DFM解决了“应该” 方面,而DRC解决了“可以”。专门解决制造问题称为制造设计(DFF),在设计过程中关注装配问题称为装配设计 (DFA)。它们共同构成了DFM分析过程。

设计人员通常依靠制造商对其设计进行DFM检查,相信制造商可以自己解决大多数问题,并仅报告那些绝对需 要设计修订的问题。这种标准过程可能会导致重大延迟,并将质量,产量和价格完全留给制造商确定。在交接之前 在内部执行DFM可以节省时间,并且您可以保留影响价格 和质量的关键设计参数的所有权。那么,为什么内部DFM分析并不总是设计到制造工作流程中必需和标准的一部分呢?关于DFM有几个常见的误解,可能会阻止设计人员将 其采用到他们的工作流程中。

设计人员在DFM方面犯的第一个常见错误是将其视为在设计过程之外发生的测试清单。相反,DFM应尽早进行,并在布局期间尽可能频繁地执行。在设计阶段早期集成DFM使设计人员能够在设计错误陷入PCB布局并难以解决之前避免设计错误。随着PCB变得越来越复杂,DFM应 该被用作设计指南,而不是在主要工作完成后要进行的修复清单。除了遵守DRC之外,运行DFM检查还可以使设计人员能够及早了解产品生命周期后期可能遇到的问题,并 使他们能够通过智能设计绕过这些问题。

另一个常见的误解是,将DFM添加到布局阶段是对DRC的耗时且昂贵的补充。将设计移交给制造并等待DFM 结果决定和澄清更改,重新设计并再次移交直到满足制造标准的传统工作流程只会使这一神话永久化。在交接之前 在内部执行DFM可以消除迭代之间的额外等待时间,从而节省大量时间,并且设计可以到达制造商的收件箱,准备进行最终批准和生产。

内部DFM的软件成本被消除respins所节省的时间和 资源所抵消,并且现在可以使用新的在线DFM产品,例如 Siemens PCBflow,这进一步降低了成本,并提供了按使用付费的模式,这些模型通常对小型企业更具成本效益。

另一个失误是将设计错误的识别和解决留给制造商,这通常是由于人们认为很难识别关键问题。在过去,DFM的价值可能已经丢失了,因为提供了太多的信息,而未能提供一种过滤和轻松标记最重要的缺陷的方法。传统上,设 计师很难猜测制造商将指定什么作为他们的顶级DFM关注点,因为制造工程需要化学和机械工艺的技能和知识,超出了大多数设计师的角色范围。

然而,业界已经推动DFM适应新的复杂程度,当今独具慧眼的设计人员可以找到一种DFM解决方案,该解决方案可提供更清晰,更集中的发现,并提供可操作的信息来解决违规行为。增强的协作使制造商能够清楚地传达其特 定的限制和要求,设计人员现在可以采用量身定制的DFM 来预测和解决其首选制造商的可制造性问题。

工业4.0正在加快从设计到市场的生命周期,设计人员受到严格的产品发布时间表的压力。在当今的市场中,如果将分析推迟到移交前的最后阶段,则在完全分析和优化之前将设计发送给制造可能是很诱人的。在讨论DRC和DFM之间的区别时,请记住,DFM(与DRC相比)发现的故障可能并不总是出现在单个或低容量原型中。然而,随着体积的增加,对于尚未经过DFM分析的设计来说,可预防的质量和良率问题将变得明显。值得庆幸的是,工业 4.0还为通信和效率提供了新的工具,并开放了虚拟协作空间。更快,更易于访问的DFM是这场革命的一部分。

集成内部DFM分析已经是企业公司的常见做法。使用 功能强大的本地解决方案为企业公司提供了减少项目持续 时间、降低风险、提高收益以及通常更快、更自信地进入市场的奢侈和便利。大公司通常有技术人员随时指导设计 师完成DFM流程,并提供有关制造技术的持续建议。较小 的企业往往会回避他们认为价格遥不可及的高端产品。他 们不必要地阻止执行DFM,并通过他们的设计工具使用任何DRC。

为了满足这些中小型企业的需求,西门子推出了 PCBflow。这种新解决方案提供了一种基于在线订阅的DFM 解决方案,该解决方案由Valor NPI引擎提供支持,并由实 际制造商定义的DFM规则提供动力。通过免费注册和会员 资格,PCBflow提供了独特的协作机会。使用此选项,设计人员可以根据需要实现DFM,并利用社区的力量与制造商建立联系,从本质上将市场带入设计以及将设计推向市场。

案例研究

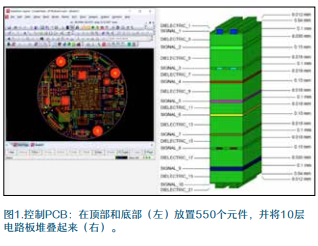

西门子慕尼黑研发机构的研究人员通过PCBflow工具运行了不同的PCB设计。以下是他们首次将PCBflow用于控制 PCB的示例描述,控制PCB是具有许多传感器和机械组件 的系统中的中央控制单元。由于系统内空间有限,电路板 轮廓为圆形,直径为70.5mm。在这个小磁盘上,必须在两侧放置550个具有2,838个引脚的组件。为了布线这么多 组件,其中包括细间距有源器件(球栅阵列低至0.5mm间 距)和小型无源器件(低至0201封装尺寸),必须采用高密度板(HDI)结构。电路板设计是使用Xpedition布局系统完成的。

图1显示了元件的位置和电路板结构。该板由一个八层 内核组成,每侧有一个顺序堆积层。顶层和底层与核心之 间的连接是盲孔。埋设的过孔连接核心内的不同内层。 在将数据发送给PCB供应商之前,他们根据DFM配置文件验证了PCB设计。他们将保存为ODB++压缩文件的设 计上传到PCBflow服务,并选择了首选PCB制造商的DFM配置文件。制造商仪表板显示公司和位置以及DFM配置文件 的名称和状态。状态为“公共”的配置文件可供所有用户 使用。状态为“受限”的配置文件属于我们在PCBflow网络 中连接到的公司。

下一步是单击“运行DFM”按钮以启动分析过程。一 旦DFM分析进度条达到100%,DFM报告就会自动呈现。对这款复杂的HDI板进行完整分析仅用了90秒。

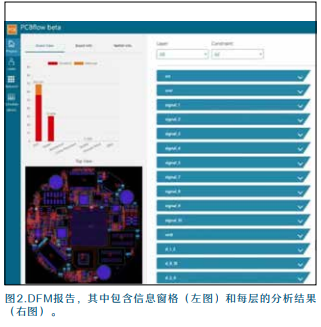

图2中所示的DFM报告是交互式的,允许筛选和滚动选项。DFM报告由两个窗格组成。信息窗格包含有关电路板 的一般信息以及从ODB++设计数据派生的错误统计信息。 结果窗格将分析结果显示为树,并提供用于查看和导出结 果的控件。

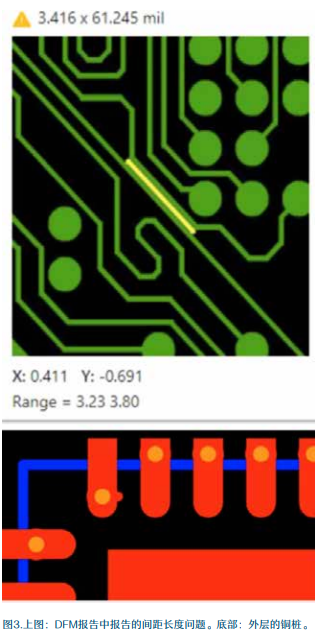

控制PCB的DFM检查确定了一系列可能在电路板生产 或组装过程中产生问题的问题。首先,他们看到信号层3 上报告两条轨道之间的长距离铜间距减小。提供了实际值 (3.416 x 61.245 mil)和误差的x,y位置等详细信息(图 3顶部)。他们很高兴能够在按下信息按钮时看到约束的描 述。根据约束容差范围,严重性评估为“黄色=警告”。这 告诉他们,除非轨道之间的距离增加,否则PCB制造商可能会因电气短路而出现严重的良率问题。DFM分析在外层检 测到几个不需要的存根(图3底部)。

由于相邻铜结构之间的距离大于设计规则检查(DRC) 中设置的值,因此在电路板布局期间无法识别这些布线伪影。而且,由于SMD焊盘的间距仅为0.5mm,因此这些铜“鼻子”在组件组装过程中会产生焊桥。结果,他们删 除了所有报告的铜桩。

还报告了一些关于存根过孔的警告。核心层2和9层之 间的埋设过孔仅连接在一侧。这些过孔是无用的,会导致明显的信号衰减,并导致更高的钻井成本。他们可以通过去除那些埋藏的过孔来提高我们设计的质量。

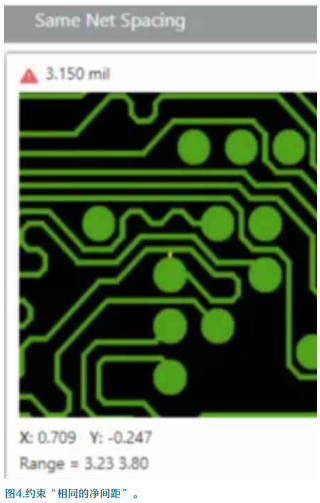

在第3层上报告了违反约束“相同净间距”的情况(图4)。同一网的铜结构之间的小空间会产生一个酸阱。酸阱有可能捕获化学蚀刻剂,用于在制造过程中从电路板上剥离多余的铜。当蚀刻溶液在特定区域汇合时,存在迹线 腐蚀和产生错误连接或开路的风险。因此,他们更改了路 线,同时牢记长度匹配要求。

研究人员在该电路板上运行DFM分析的经验,以及在 PCBflow中的许多其他实验表明,他们可以在很短的时间内改进设计,而无需在布局阶段与PCB制造商进行任何交互。

总之,我们已经看到,将DFM添加到您当前的DRC检 查中是一个价值和质量主张。这个过程现在可供所有设计师使用,并且不应该因为对价格,时间或难度的常见误解而放弃。